## **Very Short Answer:**

- (1) (2) What is the relationship between speculation and power consumption?

- (2) (2) If you are mainly worried about program size, what type of instruction set would you use? What if performance was your primary concern?

- (3) (1) Which is more effective, dynamic or static branch prediction?

- (4) (1) Do benchmarks remain valid indefinitely?

- (5) (2) Issuing multiple instructions per cycle puts tremendous pressure on what two parts of the machine?

- (6) (2) In class we mentioned VLIW and Superscalar as two ways to circumvent the Flynn Limit of 1.We also talked about two other approaches what were they?

- (7) (2) Out of Order completion makes supporting what very difficult?

- (8) (1) Are wire delays or transistors more likely to be the most significant limit on clock frequency in the future?

- (9) (2) Pipelining increases instruction \_\_\_\_\_ but also increases instruction \_\_\_\_\_(Fill in the blanks.)

- (10) (2) Decoupled architectures split a program into two streams. What are they?

- (11) (2) What is Amdahl's law (in words)?

- (12) (2) What is the primary difference between Scoreboarding and Tomasulo's algorithm?

## **Short Answers:**

(10) (4) Why are there multiple dies per silicon wafer? Why not just fabricate one huge die per wafer?

(11) (3) Write down the 3-term CPU performance equation developed in class.

(12) (4) What are the advantages and disadvantages of stack machines?

(13) (4)What is a predicated instruction? What are the advantages to using predicated instructions?When would you *not* want to use one?

(14) (4) What is the definition of a basic block? Why is there a desire to create larger ones?

(15) (3) There are at least two types of control flow changes that standard dynamic branch predictors have trouble with. There is a technique that works well for one of these types ... name the two types of branches, and the technique used to successfully deal with one of them.

(16) (4) Supporting precise interrupts in machines that allow out of order completion is a challenge. Briefly explain why, and give three different techniques that can be used to provide precise interrupts.

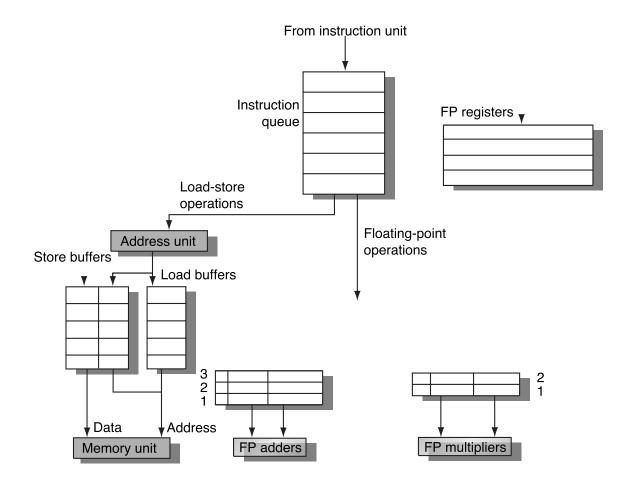

(17) (5) Why is branch prediction important? What performance enhancing techniques have made it so? List 3 examples of existing Branch Prediction strategies in order of (average) increasing effectiveness. (18) (8) Below is a picture of some of the basic components of tomasulo's algorithm. However, there are things missing. Draw in what is necessary to complete the picture.

© 2003 Elsevier Science (USA). All rights reserved.

(10) The contents of the table represent the state of the machine at time 10. Your job is to fill in the table at time 11.

|                      |             |         | In     | struction St | atus      |          |      |           |       |  |

|----------------------|-------------|---------|--------|--------------|-----------|----------|------|-----------|-------|--|

| Instruction          |             |         | Issue  |              | Execute   |          | ıte  | V         | /rite |  |

|                      | Instruction |         |        | τ            | Jnderway  | Comple   | etes | R         | esult |  |

| MULTF                | F0          | ,F2,F4  | X      |              | Х         |          |      |           |       |  |

| SUBF                 | F8          | ,F6,F2  | X      |              | Х         | Х        |      | А         | dd1   |  |

| DIVF                 | F1          | 0,F0,F6 | X      |              |           |          |      |           |       |  |

| ADDF                 | F6          | ,F8,F2  | X      |              |           |          |      |           |       |  |

| Reservation Stations |             |         |        |              |           |          |      |           |       |  |

| Tag                  | Name        | Busy    | Fm(op) | Val.j(Vj)    | Val.k(Vk) | Tag.j(Qj | )    | Tag.k(Qk) |       |  |

| Add1                 | Add/Sub     | Yes     | Sub    | Mem[]        | Mem[]     |          |      |           |       |  |

| Add2                 | Add/Sub     | Yes     | Add    | 0            | Mem[]     | Add1     |      |           |       |  |

| Add3                 | Add/Sub     |         |        |              |           |          |      |           |       |  |

| Mult1                | Mult/Div    | Yes     | Mult   | Mem[]        | Reg[F4]   |          |      |           |       |  |

| Mult2                | Mult/Div    | Yes     | Div    | 0            | Mem[]     | Add1     |      |           |       |  |

| Register Status      |             |         |        |              |           |          |      |           |       |  |

|                      | F0          | F2      | F4     | F6           | F8        | F10      | 12   |           | F30   |  |

| Tag.i(Qi)            | Mult1       |         |        | Add2         | Add1      | Mult2    |      |           |       |  |

| Time | = | 10 |  |

|------|---|----|--|

|      | _ | 10 |  |

**Time = 11**

| Instruction Status   |                 |         |        |               |          |         |           |           |       |  |

|----------------------|-----------------|---------|--------|---------------|----------|---------|-----------|-----------|-------|--|

|                      | Instruction     |         | Issue  | Issue Execute |          | Execute | V         | Vrite     |       |  |

|                      | Instruction     |         | Inst   | τ             | Jnderway |         | Completes | R         | esult |  |

| MULTF                | F0              | ,F2,F4  |        |               |          |         |           |           |       |  |

| SUBF                 | F8              | ,F6,F2  |        |               |          |         |           |           |       |  |

| DIVF                 | F1              | 0,F0,F6 |        |               |          |         |           |           |       |  |

| ADDF                 | F6              | ,F8,F2  |        |               |          |         |           |           |       |  |

| Reservation Stations |                 |         |        |               |          |         |           |           |       |  |

| Tag                  | Name            | Busy    | Fm(op) | Val.j(Vj)     | Val.k(   | Vk)     | Tag.j(Qj) | Tag.k(Qk) |       |  |

| Add1                 | Add/Sub         |         |        |               |          |         |           |           |       |  |

| Add2                 | Add/Sub         |         |        |               |          |         |           |           |       |  |

| Add3                 | Add/Sub         |         |        |               |          |         |           |           |       |  |

| Mult1                | Mult/Div        |         |        |               |          |         |           |           |       |  |

| Mult2                | Mult/Div        |         |        |               |          |         |           |           |       |  |

|                      | Register Status |         |        |               |          |         |           |           |       |  |

|                      | F0              | F2      | F4     | F6            | F8       | F10     | 12        | •••       | F30   |  |

| Tag.i(Qi)            |                 |         |        |               |          |         |           |           |       |  |

(19) (14) You are given the following code sequence:

| MULTF | F2,F1,F4 |

|-------|----------|

| SUB   | F3,F0,F1 |

| DIVF  | F2,F2,F3 |

| ADDF  | F3,F3,F2 |

Assume there are 8 logical and 16 physical registers. On the left below is the register mapping upon entering the code sequence. Your job is to fill in the mappings after the execution of the ADDF instruction, including what is on the free list. (Assume that during the execution of this code, no registers are released - in other words, the free list will be shorter at the end than at the beginning.)

| BEFORE  |          | AFTER   |          |

|---------|----------|---------|----------|

| Logical | Physical | Logical | Physical |

| 0       | 2        | 0       |          |

| 1       | 3        | 1       |          |

| 2       | 5        | 2       |          |

| 3       | 4        | 3       |          |

| 4       | 9        | 4       |          |

| 5       | 7        | 5       |          |

| 6       | 6        | 6       |          |

| 7       | 8        | 7       |          |

Free Pool: 0,1,10,11,12,13,14,15

Free Pool:

Now, rewrite the code sequence below using the actual physical register names instead of the logical ones.

| MULTF | 7 P_ | _,P_ | _,P |

|-------|------|------|-----|

| SUBF  | P_   | _,P_ | _,P |

| DIVF  | P_   | _,P_ | _,P |

| ADDF  | P_   | _,P_ | _,P |

(20) (10) Suppose we are considering two alternatives for our conditional branch instructions, as follows:

M1 - A compare is included in the branch.

M2 - A condition code is set by a compare instruction and followed by a branch that tests the condition

On both machines, the conditional branch instruction takes 2 cycles, and all other instructions take 1 cycle. On M2, 30% of all instructions executed are conditional branches. Because M2 does not have the compare included in the branch, the clock cycle is 1.20 times faster than M1.

- a. Which design is faster?

- b. What if M2 was 1.25 times faster than M1?

(21) (6) In class, we talked about the cycle by cycle steps that occur on different interrupts. For example, here is what happens if there is an illegal operand interrupt generated by instruction i+1:

|     | 1  | 2  | 3  | 4   | 5   | 6   | 7       | 8        | 9                       |

|-----|----|----|----|-----|-----|-----|---------|----------|-------------------------|

| i   | IF | ID | EX | MEM | WB  |     |         |          |                         |

| i+1 |    | IF | ID | EX  | MEM | WB  | <- Inte | rrupt de | etected                 |

| i+2 |    |    | IF | ID  | EX  | MEM | WB      | <- Inst  | ruction Squashed        |

| i+3 |    |    |    | IF  | ID  | EX  | MEM     | WB       | <- Trap Handler fetched |

| i+4 |    |    |    |     | IF  | ID  | EX      | MEM      | WB                      |

|     |    |    |    |     |     |     |         |          |                         |

Fill out the following table if instruction i experiences a fault in the execution stage (divide by zero, for example):

| 1  | 2  | 3     | 4                 | 5                                 | 6                                                                | 7                                                                                   | 8                                                                                                    | 9                                                                                                           | 10                                                                                                             |

|----|----|-------|-------------------|-----------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| IF | ID | EX    | MEM               | WB                                |                                                                  |                                                                                     |                                                                                                      |                                                                                                             |                                                                                                                |

|    | IF | ID    | EX                | MEM                               | WB                                                               |                                                                                     |                                                                                                      |                                                                                                             |                                                                                                                |

|    |    | IF    | ID                | EX                                | MEM                                                              | WB                                                                                  |                                                                                                      |                                                                                                             |                                                                                                                |

|    |    |       | IF                | ID                                | EX                                                               | MEM                                                                                 | WB                                                                                                   |                                                                                                             |                                                                                                                |

|    |    |       |                   | IF                                | ID                                                               | EX                                                                                  | MEM                                                                                                  | WB                                                                                                          |                                                                                                                |

|    |    |       |                   |                                   | IF                                                               | ID                                                                                  | EX                                                                                                   | MEM                                                                                                         | WB                                                                                                             |

|    |    | IF ID | IF ID EX<br>IF ID | IF ID EX MEM<br>IF ID EX<br>IF ID | IF ID EX MEM WB<br>IF ID EX MEM<br>IF ID EX<br>IF ID EX<br>IF ID | IF ID EX MEM WB<br>IF ID EX MEM WB<br>IF ID EX MEM<br>IF ID EX<br>IF ID EX<br>IF ID | IF ID EX MEM WB<br>IF ID EX MEM WB<br>IF ID EX MEM WB<br>IF ID EX MEM WB<br>IF ID EX MEM<br>IF ID EX | IF ID EX MEM WB<br>IF ID EX MEM | IF ID EX MEM WB<br>IF ID EX MEM WB |

What happens in this case?

|     | 1  | 2  | 3  | 4   | 5   | 6      | 7        | 8        | 9        | 10  |

|-----|----|----|----|-----|-----|--------|----------|----------|----------|-----|

| i   | IF | ID | EX | MEM | WB  | <- Dat | a write  | causes l | Page Far | ult |

| i+1 |    | IF | ID | EX  | MEM | WB     | <- Illeg | gal Opc  | ode      |     |

| i+2 |    |    | IF | ID  | EX  | MEM    | WB       |          |          |     |

| i+3 |    |    |    | IF  | ID  | EX     | MEM      | WB       |          |     |

| i+4 |    |    |    |     | IF  | ID     | EX       | MEM      | WB       |     |

| i+5 |    |    |    |     |     | IF     | ID       | EX       | MEM      | WB  |