## Lecture 8: Parallel Processing

Prof. Fred Chong

ECS 250A Computer Architecture

Winter 1999

(Adapted from Culler CS258 and Dally EE282)

FTC.W99.1

## Parallel Programming

- Motivating Problems (application case studies)

- Process of creating a parallel program

- What a simple parallel program looks like

- three major programming models

- What primitives must a system support?

FTC.W99.2

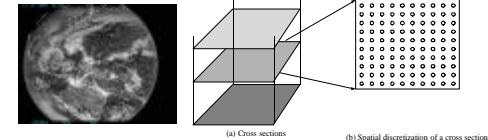

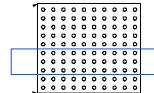

## Simulating Ocean Currents

(a) Cross sections (b) Spatial discretization of a cross section

- Model as two-dimensional grids

- Discretize in space and time

- finer spatial and temporal resolution => greater accuracy

- Many different computations per time step

- » set up and solve equations

- Concurrency across and within grid computations

- Static and regular

FTC.W99.3

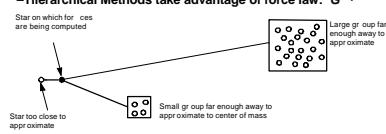

## Simulating Galaxy Evolution

- Simulate the interactions of many stars evolving over time

- Computing forces is expensive

- $O(n^2)$  brute force approach

- Hierarchical Methods take advantage of force law:  $G \frac{m_1 m_2}{r^2}$

- Many time-steps, plenty of concurrency across stars within one

FTC.W99.4

## Rendering Scenes by Ray Tracing

- Shoot rays into scene through pixels in image plane

- Follow their paths

- they bounce around as they strike objects

- they generate new rays: ray tree per input ray

- Result is color and opacity for that pixel

- Parallelism across rays

- How much concurrency in these examples?

FTC.W99.5

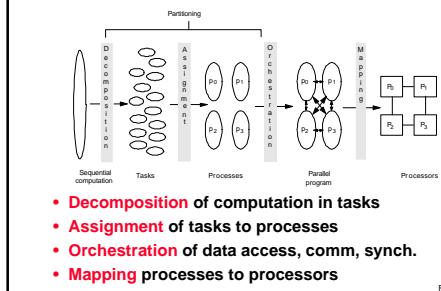

## Creating a Parallel Program

- Pieces of the job:

- Identify work that can be done in parallel

- » work includes computation, data access and I/O

- Partition work and perhaps data among processes

- Manage data access, communication and synchronization

FTC.W99.6

## Definitions

- Task:**

- Arbitrary piece of work in parallel computation

- Executed sequentially; concurrency is only across tasks

- E.g. a particle/cell in Barnes-Hut, a ray or ray group in Raytrace

- Fine-grained versus coarse-grained tasks

- Process (thread):**

- Abstract entity that performs the tasks assigned to processes

- Processes communicate and synchronize to perform their tasks

- Processor:**

- Physical engine on which process executes

- Processes virtualize machine to programmer

- write program in terms of processes, then map to processors

FTC.W99 7

## 4 Steps in Creating a Parallel Program

FTC.W99 8

## Decomposition

- Identify concurrency and decide level at which to exploit it

- Break up computation into tasks to be divided among processes

- Tasks may become available dynamically

- No. of available tasks may vary with time

- Goal: Enough tasks to keep processes busy, but not too many

- Number of tasks available at a time is upper bound on achievable speedup

FTC.W99 9

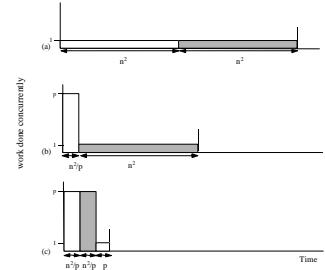

## Limited Concurrency: Amdahl's Law

- Most fundamental limitation on parallel speedup

- If fraction  $s$  of seq execution is inherently serial, speedup  $\leq 1/s$

- Example: 2-phase calculation

- sweep over  $n$ -by- $n$  grid and do some independent computation

- sweep again and add each value to global sum

- Time for first phase =  $n^2/p$

- Second phase serialized at global variable, so time =  $n^2$

- Speedup  $\leq \frac{2n^2}{\frac{n^2}{p} + n^2}$  or at most 2

- Trick: divide second phase into two

- accumulate into private sum during sweep

- add per-process private sum into global sum

- Parallel time is  $n^2/p + n^2/p + p$ , and speedup at best  $\frac{2n^2}{2n^2 + p^2}$

FTC.W99 10

## Understanding Amdahl's Law

FTC.W99 11

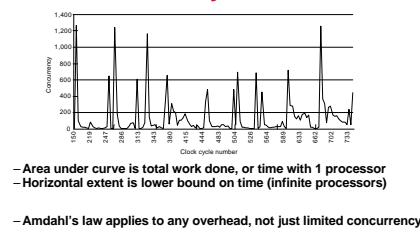

## Concurrency Profiles

FTC.W99 12

## Orchestration

- Naming data

- Structuring communication

- Synchronization

- Organizing data structures and scheduling tasks temporally

- **Goals**

- Reduce cost of communication and synch.

- Preserve locality of data reference

- Schedule tasks to satisfy dependences early

- Reduce overhead of parallelism management

- **Choices depend on Prog. Model., comm. abstraction, efficiency of primitives**

- **Architects should provide appropriate primitives efficiently**

FTC.W99 13

## Mapping

- **Two aspects:**

- Which process runs on which particular processor?

- » mapping to a network topology

- Will multiple processes run on same processor?

- **space-sharing**

- Machine divided into subsets, only one app at a time in a subset

- Processes can be pinned to processors, or left to OS

- **System allocation**

- **Real world**

- User specifies desires in some aspects, system handles some

- **Usually adopt the view: process <-> processor**

FTC.W99 14

## Parallelizing Computation vs. Data

- **Computation is decomposed and assigned (partitioned)**

- **Partitioning Data is often a natural view too**

- Computation follows data: *owner computes*

- Grid example; data mining;

- **Distinction between comp. and data stronger in many applications**

- Barnes-Hut

- Raytrace

FTC.W99 15

## Architect's Perspective

- What can be addressed by better hardware design?

- What is fundamentally a programming issue?

FTC.W99 16

## High-level Goals

| Table 2.1: Steps in the Parallelization Process and Their Goals |                         |                                                                                                                                                                                                                       |

|-----------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step                                                            | Architectural Decisions | Major Performance Goals                                                                                                                                                                                               |

| Decomposition                                                   | Mostly no               | Expose enough concurrency but not too much                                                                                                                                                                            |

| Assignment                                                      | Mostly no               | Balance workload<br>Reduce communication volume                                                                                                                                                                       |

| Orchestration                                                   | Yes                     | Reduce nonuniform communication via data locality<br>Reduce communication and synchronization cost as seen by the processor                                                                                           |

| Mapping                                                         | Yes                     | Reduce contention on shared resources<br>Reduce communication cost<br>Schedule tasks to satisfy dependences early<br>Put related processes on the same processor if necessary<br>Exploit locality in network topology |

- **High performance (speedup over sequential program)**

- **But low resource usage and development effort**

- **Implications for algorithm designers and architects?**

FTC.W99 17

## What Parallel Programs Look Like

FTC.W99 18

## Example: iterative equation solver

- Simplified version of a piece of Ocean simulation

- Illustrate program in low-level parallel language

- C-like pseudocode with simple extensions for parallelism

- Expose basic comm. and synch. primitives

- State of most real parallel programming today

Expression for updating each interior point:

$A[i,j] \leftarrow 0.2 \times (A[i,j] + A[i-1,j] + A[i+1,j] + A[i,j-1] + A[i,j+1])$

FTC.W99.19

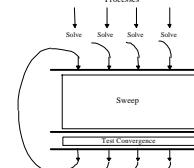

## Grid Solver

Expression for updating each interior point:

$A[i,j] \leftarrow 0.2 \times (A[i,j] + A[i-1,j] + A[i+1,j] + A[i,j-1] + A[i,j+1])$

### Gauss-Seidel (near-neighbor) sweeps to convergence

- interior n-by-n points of (n+2)-by-(n+2) updated in each sweep

- updates done in-place in grid

- difference from previous value computed

- accumulate partial diffs into global diff at end of every sweep

- check if has converged

- » to within a tolerance parameter

FTC.W99.20

## Sequential Version

```

1. int n;                                /*size of matrix: (n + 2 by n + 2) elements*/

2. float **A, diff = 0;                    /*A is an (n + 2) by (n + 2) array*/

3. main()

4. begin

5.   read(n);                            /*read input parameter: matrix size*/

6.   A = alloc((n + 2) * (n + 2), doubles); /*allocate the matrix A on heap*/

7.   initialize(A);                     /*initialize the matrix A to zero*/

8.   Solve(A);                          /*call the routine to solve equation*/

9. end main

10. procedure Solve (A)

11.   float **A;

12. begin

13.   int i, j, done = 0;                /*outermost loop over sweeps*/

14.   float temp, diff;                /*initialize maximum difference to 0*/

15.   while (!done) {

16.     diff = 0;                      /*sweep over nonborder points of grid*/

17.     for i = 1 to n do

18.       for j = 1 to n do

19.         temp = A[i,j];             /*save old value of element*/

20.         A[i,j] = 0.2 * (A[i,j] + A[i-1,j] + A[i+1,j] +

21.                           A[i,j-1] + A[i,j+1]); /*compute average*/

22.         diff += abs(A[i,j] - temp); /*accumulate partial diff into global diff*/

23.     end for

24.   end for

25.   if (diff/(n*n) < TOL) then done = 1;

26. end while

27.end procedure

```

FTC.W99.21

## Decomposition

- Simple way to identify concurrency is to look at loop iterations –dependence analysis; if not enough concurrency, then look further

- Not much concurrency here at this level (all loops sequential)

- Examine fundamental dependences

- Concurrency O(n) along anti-diagonals, serialization O(n) along diag.

- Retain loop structure, use pt-to-pt synch; Problem: too many synch ops.

- Restructure loops, use global synch; imbalance and too much synch

FTC.W99.22

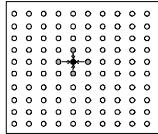

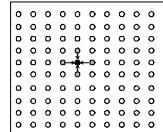

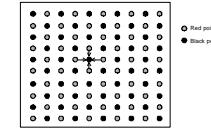

## Exploit Application Knowledge

- Reorder grid traversal: red-black ordering

- Different ordering of updates: may converge quicker or slower

- Red sweep and black sweep are each fully parallel

- Global sync between them (conservative but convenient)

- Ocean uses red-black

- We use simpler, asynchronous one to illustrate

- » no red-black, simply ignore dependences within sweep

- » parallel program nondeterministic

FTC.W99.23

## Decomposition

```

15. while (!done) do                      /*a sequential loop*/

16.   diff = 0;                            /*parallel loop nest*/

17.   for_all i ← 1 to n do

18.     for_all j ← 1 to n do

19.       temp = A[i,j];

20.       A[i,j] ← 0.2 * (A[i,j] + A[i,j-1] + A[i-1,j] +

21.                           A[i,j+1] + A[i+1,j]);

22.       diff += abs(A[i,j] - temp);

23.   end for_all

24.   if (diff/(n*n) < TOL) then done = 1;

25. end while

```

- Decomposition into elements: degree of concurrency  $n^2$

- Decompose into rows?

FTC.W99.24

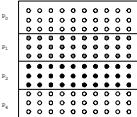

## Assignment

- **Static assignment: decomposition into rows**

- block assignment of rows: Row  $i$  is assigned to process  $p_i$

- cyclic assignment of rows: process  $i$  is assigned rows  $i, i+p, \dots$

- **Dynamic assignment**

- » get a row index, work on the row, get a new row, ...

- **What is the mechanism?**

- **Concurrency? Volume of Communication?**

FTC.W99 25

## Data Parallel Solver

```

1. int n, nprocs;           /*grid size (n+2-by-n+2) and number of processes*/

2. float **A, diff = 0;

3. main()

4. begin

5.   read(n, nprocs);      /*read input grid size and number of processes*/

6.   A = G_MALLOC(n+2, n+2); /*allocate a 2-d array of size n+2 by n+2 doubles*/

7.   initialize(A);        /*initialize the matrix A somehow*/

8.   Solve(A);             /*call the routine to solve equation*/

9. end main

10. procedure Solve(A)

11.   float **A;             /*A is an (n+2-by-n+2) array*/

12.   begin

13.     int i, j, done = 0;

14.     float mdiff = 0, temp;

15.     DECOMP_ABLOCK(*, nprocs);

16.     while (!done) do

17.       for_all i ← 1 to n do

18.         for_all j ← 1 to n do

19.           A[i,j] ← A[i,j] + A[i,j-1] + A[i-1,j] + A[i-1,j-1]; /*save old value of element*/

20.           A[i,j] ← 0.25 * (A[i,j] + A[i,j-1] + A[i-1,j] + A[i-1,j-1]); /*compute average*/

21.           temp = abs(A[i,j] - temp); /*sweep over non-border points of grid*/

22.           if (temp > mdiff) mdiff = abs(A[i,j] - temp);

23.       end for_all

24.     end while

25.     if (mdiff/nprocs < TOL) then done = 1;

26.   end procedure

27. end procedure

```

FTC.W99 26

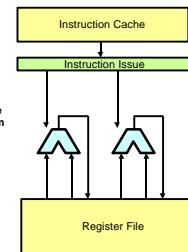

## Shared Address Space Solver

Single Program Multiple Data (SPMD)

- Assignment controlled by values of variables used as loop bounds

FTC.W99 27

## Generating Threads

```

1. int n, nprocs;           /*matrix dimension and number of processes to be used*/

2. float **A, diff;          /*A is a global (shared) array representing the grid*/

3. /*diff is global (shared) maximum difference in current sweep*/

2b. LOCKDEF diff_lock;      /*declaration of lock to enforce mutual exclusion*/

2c. BARDEC (bar1);          /*barrier declaration for global synchronization between sweeps*/

4. main()

5. begin

6.   read(n); read(nprocs); /*read input matrix size and number of processes*/

7.   A = G_MALLOC(n+2, n+2); /*allocate a 2-d array of size n+2 by n+2 doubles*/

8.   initialize(A);          /*initialize A in an unspecified way*/

8a. CREATE (nprocs-1, Solve, A); /*main process becomes a worker too*/

8b. WUTFOR_END (nprocs-1); /*wait for all child processes created to terminate*/

9. end main

10. procedure Solve(A)

11.   float **A;             /*A is entire n+2-by-n+2 shared array,

12.                                as in the sequential program*/

13.   begin

14.     int i, j, pid, done = 0;

15.     float mdiff = 0, temp = 0; /*private variables*/

16.     int mymax = 0, n = pid * nprocs;

17.     int mymin = mymax + n / nprocs - 1; /*assume that is exactly divisible by nprocs*/

18.     while (!done) do

19.       for_all i ← 1 to n do

20.         for_all j ← 1 to n do

21.           temp = 0.25 * (A[i,j] + A[i,j-1] + A[i-1,j] + A[i-1,j-1]);

22.           A[i,j] = temp;

23.           if (temp > mdiff) mdiff = abs(A[i,j] - temp);

24.       end for_all

25.     end while

26.     BARREC (bar1, nprocs); /*update global diff if necessary*/

27.   end procedure

```

FTC.W99 28

## Assignment Mechanism

```

1. procedure Solve(A)

2.   float **A;             /*A is entire n+2-by-n+2 shared array,

3.                                as in the sequential program*/

4.   begin

5.     int i, j, pid, done = 0;

6.     float mdiff = 0, temp = 0; /*private variables*/

7.     int mymax = 0, n = pid * nprocs;

8.     int mymin = mymax + n / nprocs - 1; /*assume that is exactly divisible by nprocs*/

9.     while (!done) do

10.       for_all i ← 1 to n do

11.         for_all j ← 1 to n do

12.           temp = 0.25 * (A[i,j] + A[i,j-1] + A[i-1,j] + A[i-1,j-1]);

13.           A[i,j] = temp;

14.           if (temp > mdiff) mdiff = abs(A[i,j] - temp);

15.       end for_all

16.     end while

17.     BARREC (bar1, nprocs); /*update global diff if necessary*/

18.   end procedure

```

FTC.W99 29

## SAS Program

- **SPMD: not lockstep. Not necessarily same instructions**

- **Assignment controlled by values of variables used as loop bounds**

- unique pid per process, used to control assignment

- done condition evaluated redundantly by all

- Code that does the update identical to sequential program

- each process has private mydiff variable

- **Most interesting special operations are for synchronization**

- accumulations into shared diff have to be mutually exclusive

- why the need for all the barriers?

- **Good global reduction?**

- Utility of this parallel accumulate???

FTC.W99 30

## Mutual Exclusion

- Why is it needed?

- Provided by LOCK-UNLOCK around *critical section*

- Set of operations we want to execute atomically

- Implementation of LOCK/UNLOCK must guarantee mutual excl.

- Serialization?

- Contention?

- Non-local accesses in critical section?

- use private mydiff for partial accumulation!

FTC.W99 31

## Group Event Synchronization

- Subset of processes involved

- Can use flags or barriers (involving only the subset)

- Concept of producers and consumers

- Major types:

- Single-producer, multiple-consumer

- Multiple-producer, single-consumer

- Multiple-producer, single-consumer

FTC.W99 34

## Global Event Synchronization

- BARRIER(nprocs): wait here till nprocs processes get here

- Built using lower level primitives

- Global sum example: wait for all to accumulate before using sum

- Often used to separate phases of computation

- *Process P<sub>1</sub>*      *Process P<sub>2</sub>*      *Process P<sub>nprocs</sub>*

|                        |                        |                        |

|------------------------|------------------------|------------------------|

| set up eqn system      | set up eqn system      | set up eqn system      |

| Barrier (name, nprocs) | Barrier (name, nprocs) | Barrier (name, nprocs) |

| solve eqn system       | solve eqn system       | solve eqn system       |

| Barrier (name, nprocs) | Barrier (name, nprocs) | Barrier (name, nprocs) |

| apply results          | apply results          | apply results          |

| Barrier (name, nprocs) | Barrier (name, nprocs) | Barrier (name, nprocs) |

- **Conservative form of preserving dependences, but easy to use**

- WAIT\_FOR\_END (nprocs-1)

FTC.W99 32

## Pt-to-pt Event Synch (Not Used Here)

- One process notifies another of an event so it can proceed

- Common example: producer-consumer (bounded buffer)

- Concurrent programming on uniprocessor: semaphores

- Shared address space parallel programs: semaphores, or use ordinary variables as flags

*P<sub>1</sub>*      *P<sub>2</sub>*

a: while (flag is 0) do nothing;      b: flag = 1;

print A;

• Busy-waiting or spinning

FTC.W99 33

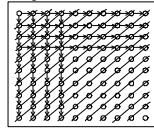

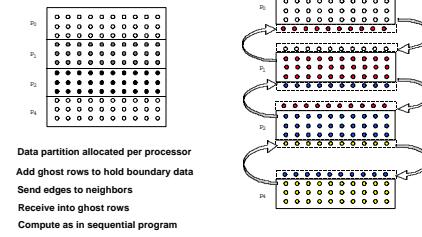

## Message Passing Grid Solver

- Cannot declare A to be global shared array

- compose it logically from per-process private arrays

- usually allocated in accordance with the assignment of work

- » process assigned a set of rows allocates them locally

- Transfers of entire rows between traversals

- Structurally similar to SPMD SAS

- Orchestration different

- data structures and data access/naming

- communication

- synchronization

- Ghost rows

FTC.W99 35

## Data Layout and Orchestration

FTC.W99 36

```

10. procedure Solver()

11. begin

12.   i,j, pid, n = n/proc, done = 0;

13.   float temp, tempdiff, mydiff = 0; /*private variables*/

14.   myA <- malloc( a 2-d array of size [n/proc] + 2] by n*2;

15.   /*Initialize myA of A, in an unspecified way*/

```

```

16.   while (!done) do

17.     mydiff = 0; /*local diff to 0*/

18.     /*Exchange 1 row of neighbors in myA[] and myB[]*/

19.     if (pid == 0) then SEND myA[1,0],n*sizeof(float),pid-1,ROW;

20.     if (pid == nproc-1) then RECEIVE myA[0,0],n*sizeof(float),pid+1,ROW;

21.     if (pid > 0) then RECEIVE myA[0,0],n*sizeof(float),pid-1,ROW;

22.     if (pid < nproc-1) then RECEIVE myA[1,0],n*sizeof(float),pid+1,ROW;

23.     /*REDUCE sumA[i+1,0],n*sizeof(float), pid+1,ROW;

24.     for i = 0 to n-1 do /*for each of my (ghost) rows*/

25.       for j = 0 to n-1 do /*for all nonborder elements in that row*/

26.         top = myA[i,j];

27.         myA[i,j] = myA[i,j] + myA[i,j-1] + myA[i-1,j];

28.         mydiff += abs(myA[i,j] - temp;

29.       endfor;

30.     endfor;

31.   /*communicate local diff values and determine if done, can be replaced by reduction and broadcast*/

32.   if (pid == 0) then

33.     SEND mydiff,n*sizeof(float),0,DONE;

34.   else

35.     RECEIVE done,n*sizeof(int),0,DONE; /*pid 0 does this*/

36.   for i = 1 to nproc-1 do /*for each other process*/

37.     if (pid == i) then

38.       ADD mydiff,tempdiff,n*sizeof(float), /*DONE*/

39.       mydiff = tempdiff;

40.   endfor;

41.   if (mydiff/(n*n) < TOL) then done = 1;

42.   for i = 1 to nproc-1 do /*for each other process*/

43.     SEND done,n*sizeof(int),i,DONE;

44.   endfor;

45.   /*done*/

46.   endwhile;

47. end procedure

```

FTC.W99 37

## Notes on Message Passing Program

- Use of ghost rows

- Receive does not transfer data, send does

- unlike SAS which is usually receiver-initiated (load fetches data)

- Communication done at beginning of iteration, so no asynchrony

- Communication in whole rows, not element at a time

- Core similar, but indices/bounds in local rather than global space

- Synchronization through sends and receives

- Update of global diff and event sync for done condition

- Could implement locks and barriers with messages

- Can use REDUCE and BROADCAST library calls to simplify code

```

25a. /*communicate local diff values and determine if done, using reduction and broadcast*/

25b. REDUCE 0,mydiff,n*sizeof(float),ADD;

25c. if (pid == 0) then

25d.   if (mydiff/(n*n) < TOL) then done = 1;

25e.   endif;

25f. BROADCAST 0,done,n*sizeof(int),DONE;

```

FTC.W99 38

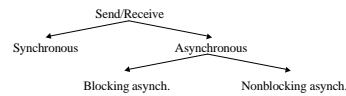

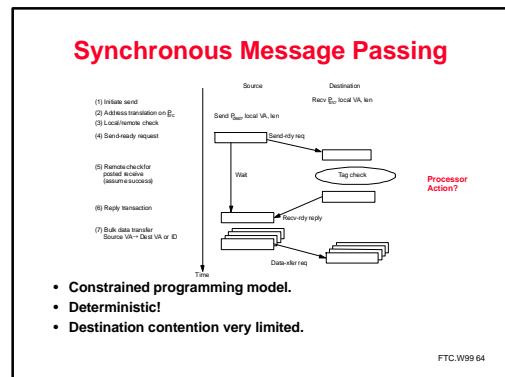

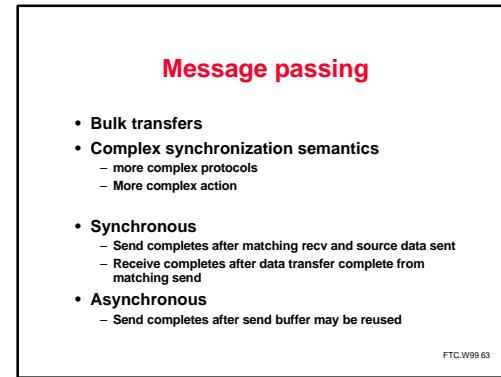

## Send and Receive Alternatives

Can extend functionality: stride, scatter-gather, groups

Semantic flavors: based on when control is returned

Affect when data structures or buffers can be reused at either end

- Affect event sync (mutual excl. by flat: only one process touches data)

- Affect ease of programming and performance

- Synchronous messages provide built-in sync. through match

- Separate event synchronization needed with asynch. messages

- With sync. messages, our code is deadlocked. Fix?

FTC.W99 39

## Orchestration: Summary

- Shared address space

- Shared and private data explicitly separate

- Communication implicit in access patterns

- No correctness need for data distribution

- Synchronization via atomic operations on shared data

- Synchronization explicit and distinct from data communication

- Message passing

- Data distribution among local address spaces needed

- No explicit shared structures (implicit in comm. patterns)

- Communication is explicit

- Synchronization implicit in communication (at least in synch. case)

- » mutual exclusion by flat

FTC.W99 40

## Correctness in Grid Solver Program

|                                      | SAS      | Msg-Passing |

|--------------------------------------|----------|-------------|

| Explicit global data structure?      | Yes      | No          |

| Assignment indept of data layout?    | Yes      | No          |

| Communication                        | Implicit | Explicit    |

| Synchronization                      | Explicit | Implicit    |

| Explicit replication of border rows? | No       | Yes         |

- Decomposition and Assignment similar in SAS and message-passing

- Orchestration is different

- Data structures, data access/naming, communication, synchronization

- Performance?

FTC.W99 41

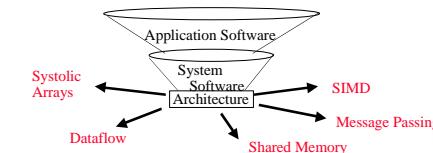

## History of Parallel Architectures

- Parallel architectures tied closely to programming models

- Divergent architectures, with no predictable pattern of growth.

- Mid 80s renaissance

FTC.W99 42

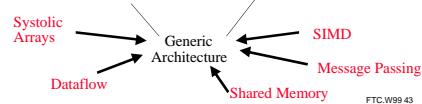

## Convergence

- Look at major programming models

- where did they come from?

- The 80s architectural renaissance!

- What do they provide?

- How have they converged?

- Extract general structure and fundamental issues

- Reexamine traditional camps from new perspective

FTC.W99.43

## Programming Model

- *Conceptualization of the machine that programmer uses in coding applications*

- How parts cooperate and coordinate their activities

- Specifies communication and synchronization operations

- **Multiprogramming**

- no communication or synch. at program level

- **Shared address space**

- like bulletin board

- **Message passing**

- like letters or phone calls, explicit point to point

- **Data parallel**

- more regimented, global actions on data

- Implemented with shared address space or message passing

FTC.W99.44

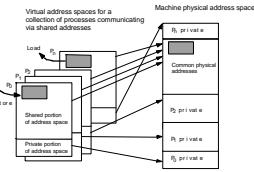

## Structured Shared Address Space

FTC.W99.45

- Add hoc parallelism used in system code

- Most parallel applications have structured SAS

- Same program on each processor

- shared variable X means the same thing to each thread

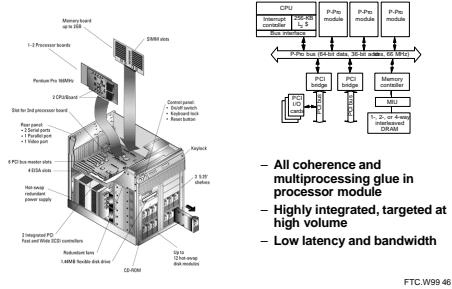

## Engineering: Intel Pentium Pro Quad

FTC.W99.46

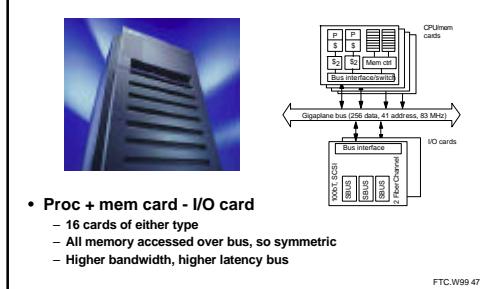

## Engineering: SUN Enterprise

FTC.W99.47

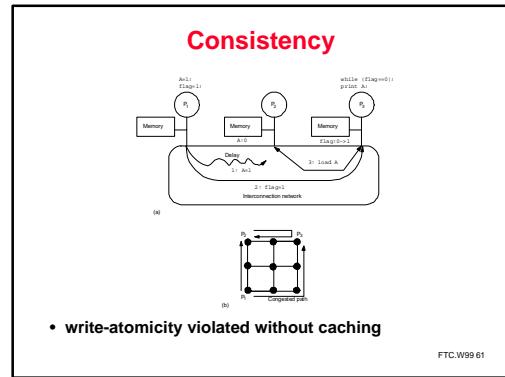

## Scaling Up

- Problem is interconnect: cost (crossbar) or bandwidth (bus)

- Dance-hall: bandwidth still scalable, but lower cost than crossbar

- » latencies to memory uniform, but uniformly large

- Distributed memory or non-uniform memory access (NUMA)

- » Construct shared address space out of simple message transactions across a general-purpose network (e.g. read-request, read-response)

- Caching shared (particularly nonlocal) data?

FTC.W99.48

### Engineering: Cray T3E

- Scale up to 1024 processors, 480MB/s links

- Memory controller generates request message for non-local references

- No hardware mechanism for coherence

- » SGI Origin etc. provide this

FTC.W99 49

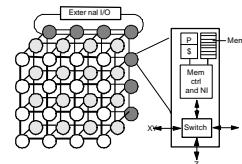

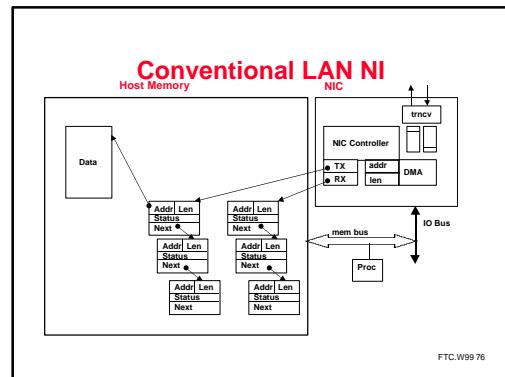

### Message Passing Architectures

- Complete computer as building block, including I/O

- Communication via explicit I/O operations

- Programming model

- direct access only to private address space (local memory),

- communication via explicit messages (send/receive)

- High-level block diagram

- Communication integration?

- » Mem, I/O, LAN, Cluster

- Easier to build and scale than SAS

- Programming model more removed from basic hardware operations

- Library or OS intervention

FTC.W99 50

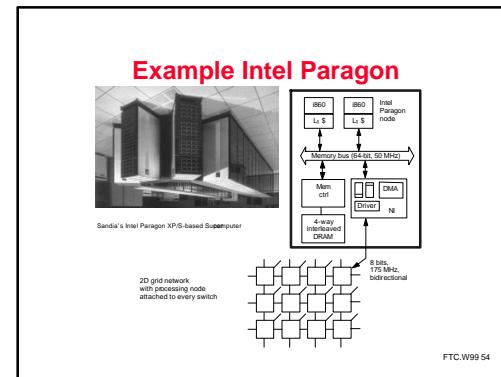

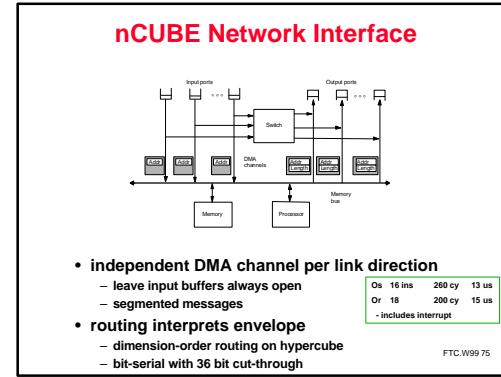

### Evolution of Message-Passing Machines

- Early machines: FIFO on each link

- HW close to prog. Model;

- synchronous ops

- topology central (hypercube algorithms)

CalTech Cosmic Cube (Seitz, CACM Jan 95)

FTC.W99 52

### Diminishing Role of Topology

- Shift to general links

- DMA, enabling non-blocking ops

- » Buffered by system at destination until recv

- Store&forward routing

- Diminishing role of topology

- Any-to-any pipelined routing

- node-network interface dominates communication time

|                       |    |                  |

|-----------------------|----|------------------|

| $H \times (T_s + nB)$ | vs | $T_0 + H_A + nB$ |

|-----------------------|----|------------------|

- Simplifies programming

- Allows richer design space

- » grids vs hypercubes

Intel iPSC/1 -> iPSC/2 -> iPSC/860

FTC.W99 53

**Building on the mainstream: IBM SP-2**

- Made out of essentially complete RS6000 workstations

- Network interface integrated in I/O bus (bw limited by I/O bus)

General I/O connection block

8-port switches

IBM SP-2 node

PowerPC CPU

Memory controller

4-way memory bus

Memory controller

DRAM

I/O

SCSI

NIC

HBA

FTC.W99 55

**Berkeley NOW**

- 100 Sun Ultra2 workstations

- Intelligent network interface

- proc + mem

- Myrinet Network

- 160 MB/s per link

- 300 ns per hop

FTC.W99 56

**Toward Architectural Convergence**

- Evolution and role of software have blurred boundary

- Send/recv supported on SAS machines via buffers

- Can construct global address space on MP (GA -> P | LA)

- Page-based (or finer-grained) shared virtual memory

- Hardware organization converging too

- Tighter NI integration even for MP (low-latency, high-bandwidth)

- Hardware SAS passes messages

- Even clusters of workstations/SMPs are parallel systems

- Emergence of fast system area networks (SAN)

- Programming models distinct, but organizations converging

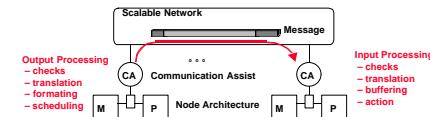

- Nodes connected by general network and communication assists

- Implementations also converging, at least in high-end machines

FTC.W99 57

**Programming Models Realized by Protocols**

CAD Database Scientific modeling Parallel applications

Multiprogramming Shared address Message passing Data parallel

Programming models

Operating systems support

Communication abstraction User/system boundary

Communication hardware

Physical communication medium

Network Transactions

FTC.W99 58

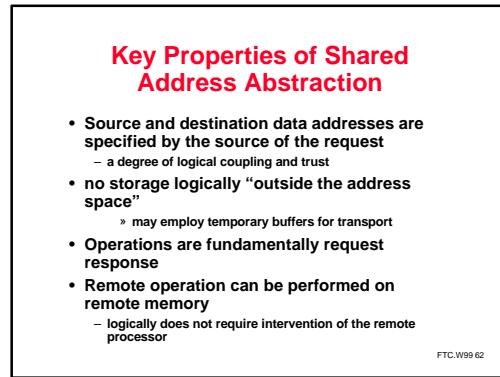

**Shared Address Space Abstraction**

- Initiate memory access

- Address translation

- Local remote check

- Request in transaction

- Read request

- Memory access

- Read response

- Read response

- Complete memory access

Source

Destination

Load r1 -> [Global address]

Read request

Memory access

Read response

Read response

Time

FTC.W99 59

- Fundamentally a two-way request/response protocol

- writes have an acknowledgement

- Issues

- fixed or variable length (bulk) transfers

- remote virtual or physical address, where is action performed?

- deadlock avoidance and input buffer full

- coherent? consistent?

**The Fetch Deadlock Problem**

- Even if a node cannot issue a request, it must sink network transactions.

- Incoming transaction may be a request, which will generate a response.

- Closed system (finite buffering)

FTC.W99 60

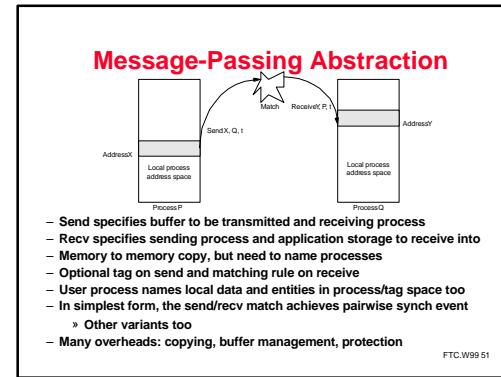

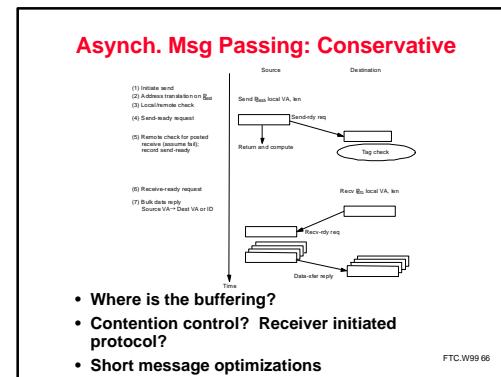

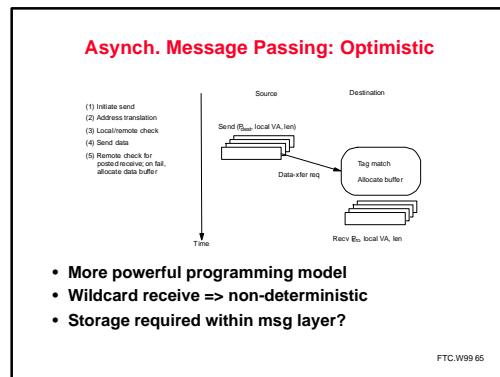

## Key Features of Msg Passing Abstraction

- Source knows send data address, dest. knows receive data address

- after handshake they both know both

- Arbitrary storage “outside the local address spaces”

- may post many sends before any receives

- non-blocking asynchronous sends reduces the requirement to an arbitrary number of descriptors

- » fingerprint says these are limited too

- Fundamentally a 3-phase transaction

- includes a request / response

- can use optimistic 1-phase in limited “Safe” cases

- » credit scheme

FTC.W99.67

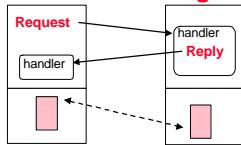

## Active Messages

- User-level analog of network transaction

- transfer data packet and invoke handler to extract it from the network and integrate with on-going computation

- Request/Reply

- Event notification: interrupts, polling, events?

- May also perform memory-to-memory transfer

FTC.W99.68

## Common Challenges

- Input buffer overflow

- N-1 queue over-commitment => must slow sources

- reserve space per source (credit)

- » when available for reuse?

- Ack or Higher level

- Refuse input when full

- » backpressure in reliable network

- » tree saturation

- » deadlock free

- » what happens to traffic not bound for congested dest?

- Reserve ack back channel

- drop packets

- Utilize higher-level semantics of programming model

FTC.W99.69

## Challenges (cont)

- Fetch Deadlock

- For network to remain deadlock free, nodes must continue accepting messages, even when cannot source msgs

- » what if incoming transaction is a request?

- Each may generate a response, which cannot be sent!

- What happens when internal buffering is full?

- logically independent request/reply networks

- physical networks

- virtual channels with separate input/output queues

- bound requests and reserve input buffer space

- $K(P-1)$  requests +  $K$  responses per node

- service discipline to avoid fetch deadlock?

- NACK on input buffer full

- NACK delivery?

FTC.W99.70

## Challenges in Realizing Prog. Models in the Large

- One-way transfer of information

- No global knowledge, nor global control

- barriers, scans, reduce, global-Or give fuzzy global state

- Very large number of concurrent transactions

- Management of input buffer resources

- many sources can issue a request and over-commit destination before any see the effect

- Latency is large enough that you are tempted to “take risks”

- optimistic protocols

- large transfers

- dynamic allocation

- Many many more degrees of freedom in design and engineering of these system

FTC.W99.71

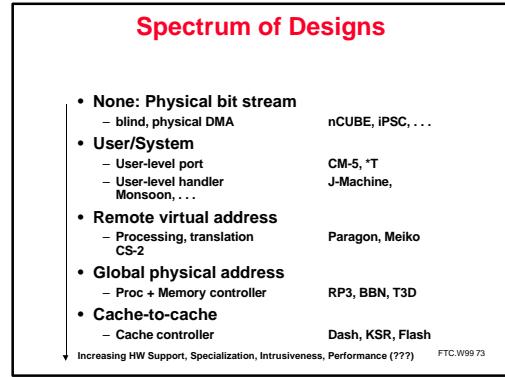

## Network Transaction Processing

- Key Design Issue:

- How much interpretation of the message?

- How much dedicated processing in the Comm. Assist?

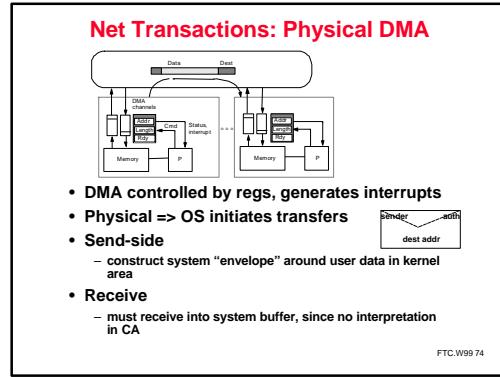

FTC.W99.72

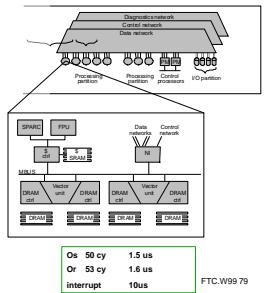

### Example: CM-5

- Input and output FIFO for each network

- 2 data networks

- index NI mapping table

- context switching?

- \*T integrated NI on chip

- iWARP also

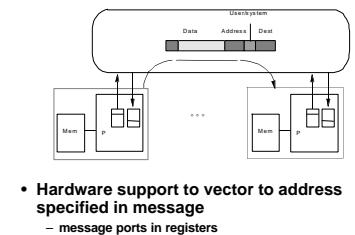

### User Level Handlers

### J-Machine: Msg-Driven Processor

- Each node a small msg driven processor

- HW support to queue msgs and dispatch to msg handler task

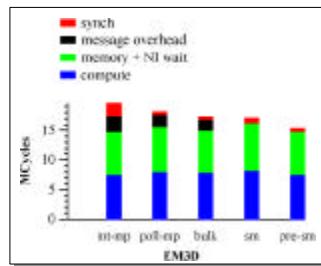

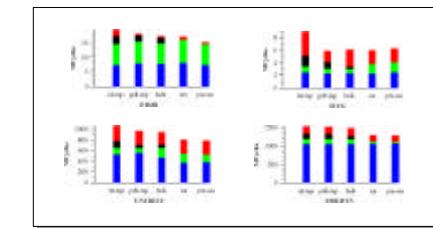

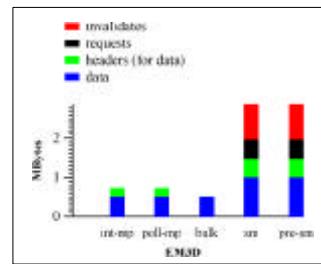

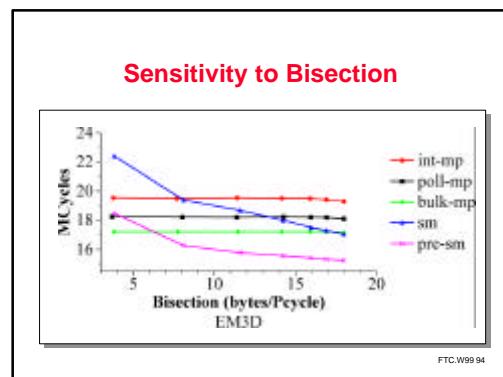

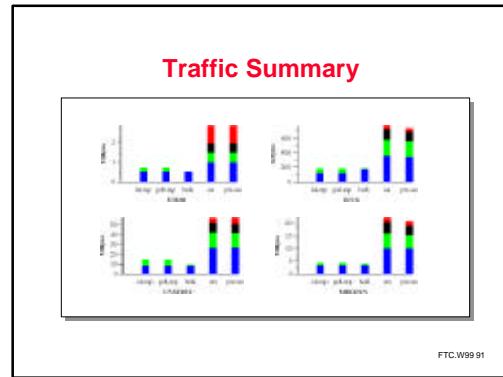

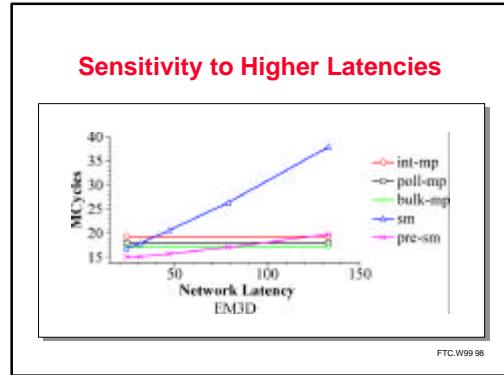

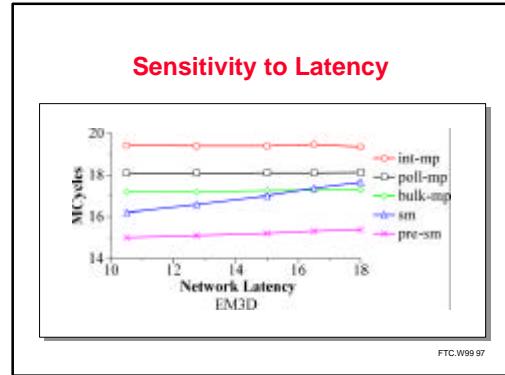

### Communication Comparison

- Message passing (active messages)

- interrupts (int-mp)

- polling (poll-mp)

- bulk transfer (bulk)

- Shared memory (sequential consistency)

- without prefetching (sm)

- with prefetching (pre-sm)

FTC.W99.82

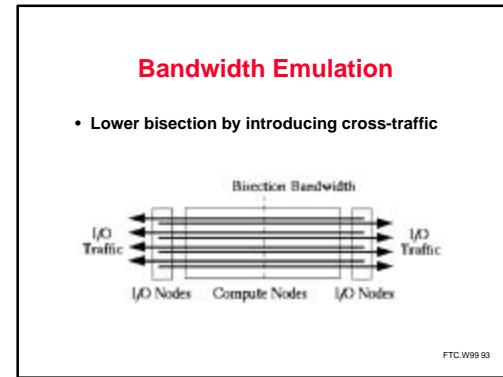

### Motivation

- Comparison over a range of parameters

- latency and bandwidth emulation

- hand-optimized code for each mechanism

- » 5 versions of 4 applications

FTC.W99.83

### The Alewife Multiprocessor

FTC.W99.84

### Alewife Mechanisms

- Int-mp -- 100-200 cycles Send/Rec ovrhd

- Poll-mp -- saves 50-170 cycles Rec ovrhd

- Bulk -- gather/scatter

- Sm -- 42-63 cycles + 1.6 cycles/hop

- Pre-sm -- 2 cycles, 16 entry buffer

FTC.W99.85

### Applications

- Irregular Computations

- Little data re-use

- Data driven

FTC.W99.86

### Application Descriptions

|         |                            |

|---------|----------------------------|

| EM3D    | 3D electromagnetic wave    |

| ICCG    | irreg sparse matrix solver |

| Unstruc | 3D fluid flow              |

| Moldyn  | molecular dynamics         |

FTC.W99.87

### Performance Breakdown

FTC.W99.88

### Performance Summary

FTC.W99.89

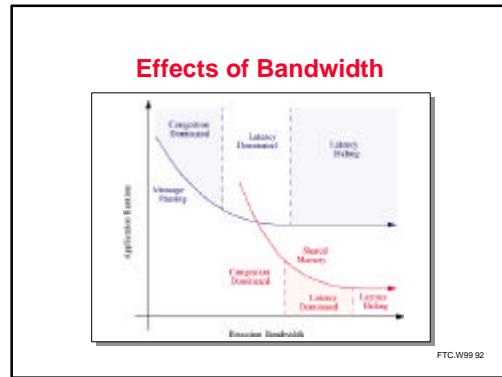

### Traffic Breakdown

FTC.W99.90

### Communication Comparison Summary

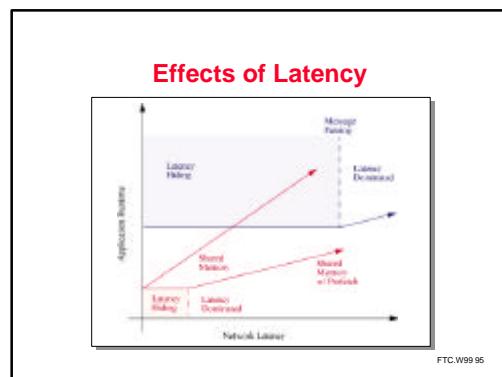

- Low overhead in shared memory performs well even with:

- irregular, data-driven applications

- little re-use

- Bisection and latency can cause crossovers

FTC.W99 99

### Future Technology

- Technology changes the cost and performance of computer elements in a non-uniform manner

- logic and arithmetic is becoming plentiful and cheap

- wires are becoming slow and scarce

- This changes the tradeoffs between alternative architectures

- superscalar doesn't scale well

- global control and data

- So what will the architectures of the future be?

FTC.W99 100

### Single-Chip Multiprocessors

- Build a multiprocessor on a single chip

- linear increase in peak performance

- advantage of fast interaction between processors

- But

- memory bandwidth problem multiplied

FTC.W99 101

### Exploiting fine-grain threads

- Where will the parallelism come from to keep all of these processors busy?

- ILP - limited to about 5

- Outer-loop parallelism

- e.g., domain decomposition

- requires big problems to get lots of parallelism

- Fine threads

- make communication and synchronization very fast (1 cycle)

- break the problem into smaller pieces

- more parallelism

FTC.W99 102

## Processor with DRAM (PIM)

- Put the processor and the main memory on a single chip

- much lower memory latency

- much higher memory bandwidth

- But

- need to build systems with more than one chip

64Mb SDRAM Chip

Internal - 128 512K subarrays

4 bits per subarray each 10ns

51.2 Gb/s

External - 8 bits at 10ns, 800Mb/s

1 Integer processor ~ 100KBytes DRAM

1 FP processor ~ 500KBytes DRAM

FTC.W99 103

## Reconfigurable processors

- Adapt the processor to the application

- special function units

- special wiring between function units

- Builds on FPGA technology

- FPGAs are inefficient

- a multiplier built from an FPGA is about 100x larger and 10x slower than a dedicated multiplier.

- Need to raise the granularity

- configure ALUs, or whole processors

- Memory and communication are usually the bottleneck

- not addressed by configuring a lot of ALUs

FTC.W99 104

## EPIC - explicit (instruction-level) parallelism aka VLIW

- Compiler schedules instructions

- Encodes dependencies explicitly

- saves having the hardware repeatedly rediscover them

- Support speculation

- speculative load

- branch prediction

- Really need to make communication explicit too

- still has global registers and global instruction issue

FTC.W99 105

## Summary

- Parallelism is inevitable

- ILP

- Medium

- Massive

- Commodity forces

- SIMPs

- NOWs, CLUMPs

- Technological trends

- MP chips

- Intelligent memory

FTC.W99 106