| 1. | (1pts) What is the Hamming distance between these two bit patterns: 1001 and 0101?                                                                                                                                                                                                                        |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | (3pts) Write the equation for the carry out of the 3rd adder cell in an ALU using carry-lookahead, in terms of P's and G's.                                                                                                                                                                               |

| 3. | (3pts) What is the difference between the Mealy and Moore models of sequential design?                                                                                                                                                                                                                    |

| 4. | (3pts) What is the difference between a Flip-Flop and a latch?                                                                                                                                                                                                                                            |

| 5. | (5pts) In the ALU you designed in the homework, how did you differentiate between an operation being an "add" and an operation being a "subtract"? In other words, what bit/bits were set/cleared in order to indicate that the values were to be added instead of subtracted? Why did this work so well? |

|    |                                                                                                                                                                                                                                                                                                           |

6. (10 pts) Assuming a rising edge-triggered DFF, what is the maximum clock frequency possible for the following circuit? (In other words, what is the maximum clock frequency that will still guarantee correct behavior?) Use the following delay values, and assume all input signals become valid at time 0. (Tprop is the propagation time for the flipflop, the time it takes from the rising edge of the clock until the output of the FF is valid.)

AND: 3 ns NAND: 7ns MUX:6 ns Tprop: 5 ns Tsetup: 2ns Thold: 1ns

7. (3pts) How far apart must valid code words be to allow Double Error Detection (DED)? Quadruple Error Correction (QEC)? Five-tuple (5) Error Correction sex-tuple (6) Error Detection (FECQED)?

8. (12 pts) Assume you have 8-bit data words, and your memory system supports Single Error Correction. For each of the following patterns recieved from memory identify and correct any errors that may have occurred during transmission or storage. Assume the same organization of carry and data bits as we used in class. The first one is done for you.

Given: **0 0 1 0 1 1 0 1 0 1 1 1** The Data Word is: **00101011**

Given: **011111100000** The Data Word is:

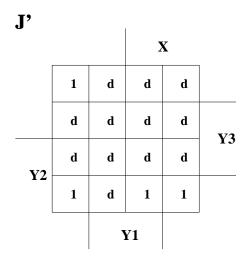

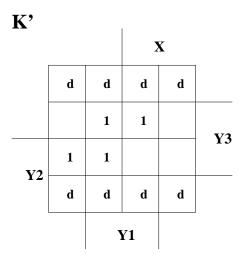

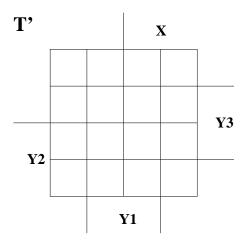

9. (5 pts) You have derived the following karnaugh maps for the inputs to an JK flp-fbp. Unfortunately, the parts department just called and your company is completely out of JK flp-fbps. All they have left in stock is T flp-fbps, which you will have to use instead. Show the resulting karnaugh map for the modified version of the circuit (the one that uses the T instead of the JK flp-fbp.) You do **not** have to write down the minimized equation.

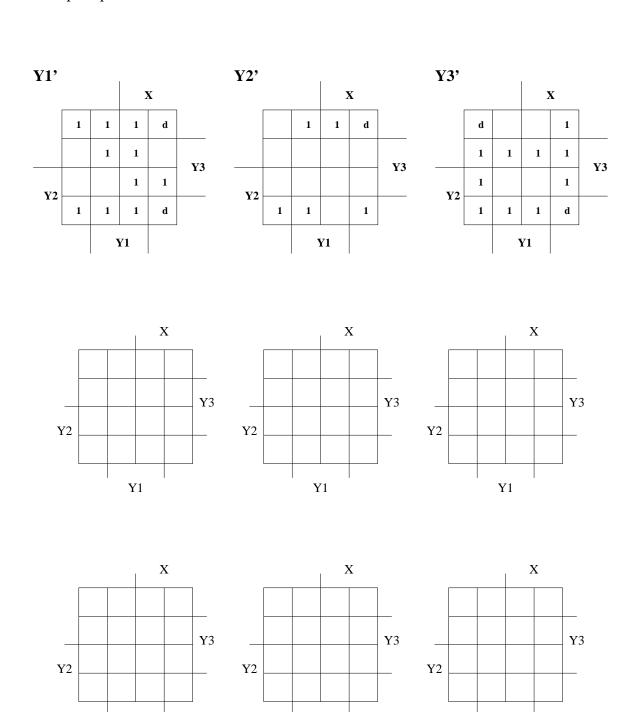

10. (20) Given the following table, draw the Karnaugh maps for Y1', Y2', and Y3' and Z in terms of X, Y1, Y2 and Y3, and then write **minimum** boolean equations for each.

| Present    | Next          | Output        |     |     |

|------------|---------------|---------------|-----|-----|

| State      | X=0           | X=1           | X=0 | X=1 |

| (Y1 Y2 Y3) | (Y1' Y2' Y3') | (Y1' Y2' Y3') |     |     |

| 000        | 011           | 011           | 0   | 0   |

| 010        | 011           | 011           | 0   | 1   |

| 011        | 010           | 010           | 0   | 0   |

| 100        | 100           | 100           | 0   | 0   |

| 101        | 010           | 010           | 1   | 1   |

| 110        | 100           | 100           | 0   | 1   |

| 111        | 100           | 100           | 1   | 1   |

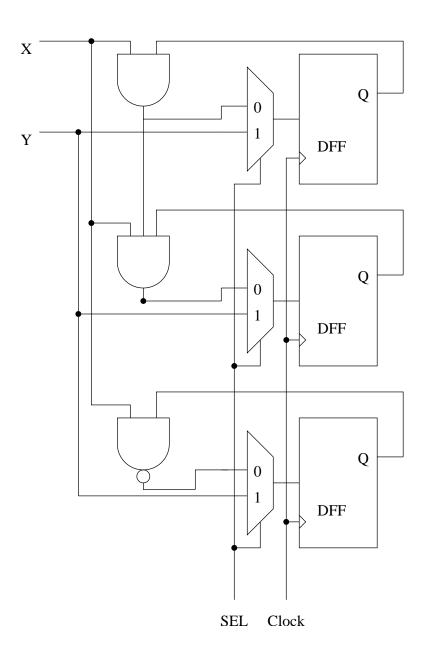

11. (15 pts) Given the following Karnaugh maps, implement the sequential machine using an SR FF for Y1, a JK FF for Y2, and a T FF for Y3. You do not need to draw the gates, but you do need to write down the **minimized** input equations for each of the inputs of each of the Flip Flops in the circuit.

Y1

Y1

Y1

12. (20 pts) The President of Freedonia, Rufus T. Firefly, wants to add a Sprite machine to his living quarters. The machine he prefers accepts two coins, the 5 Quatloo piece and the 15 Quatloo piece. Each can costs 20 Quatloos. The machine must give change, because the President is a cheapskate. Let X1=15 Quatloo coin and X2=5 Quatloo coin, and assume both coins cannot be inserted simultaneously. Also assume that if you are stupid enough to put in 3 "nickquels" and then a 15 Quatloo piece, or two 15 Quatloo pieces in a row, you will pay a 5 Quatloo penalty and only get 1 "nickQuel" back (because the President has the key to the Sprite machine anyway.)

Draw the State Transistion Diagram (the circles and the arcs) for this finite state machine. Let S0=no money input (the Start state). Once you have a state transition diagram, minimize the number of states necessary and then assign bit patterns to each state and write down the corresponding state transition table. Assume you are using a Mealy model. Label the transitions on the diagram using the format we used in class (inputs over outputs).